### **Molecular Crystals and Liquid Crystals**

ISSN: 1542-1406 (Print) 1563-5287 (Online) Journal homepage: http://www.tandfonline.com/loi/gmcl20

# Address Discharge Characteristics by Changes in Sustain Pulse Numbers in Plasma Display Panel with High Xe Contents

Hyun-Jin Kim, Jae Hyun Kim, Byung-Tae Choi & Heung-Sik Tae

**To cite this article:** Hyun-Jin Kim, Jae Hyun Kim, Byung-Tae Choi & Heung-Sik Tae (2015) Address Discharge Characteristics by Changes in Sustain Pulse Numbers in Plasma Display Panel with High Xe Contents, Molecular Crystals and Liquid Crystals, 617:1, 158-167, DOI: 10.1080/15421406.2015.1075848

To link to this article: <a href="http://dx.doi.org/10.1080/15421406.2015.1075848">http://dx.doi.org/10.1080/15421406.2015.1075848</a>

Full Terms & Conditions of access and use can be found at http://www.tandfonline.com/action/journalInformation?journalCode=gmcl20

Mol. Cryst. Liq. Cryst., Vol. 617: pp. 158–167, 2015 Copyright © Taylor & Francis Group, LLC

ISSN: 1542-1406 print/1563-5287 online DOI: 10.1080/15421406.2015.1075848

## Address Discharge Characteristics by Changes in Sustain Pulse Numbers in Plasma Display Panel with High Xe Contents

# HYUN-JIN KIM,<sup>1</sup> JAE HYUN KIM,<sup>2</sup> BYUNG-TAE CHOI,<sup>3</sup> AND HEUNG-SIK TAE<sup>1,\*</sup>

<sup>1</sup>School of Electronics Engineering, College of IT Engineering, Kyungpook National University, Daegu, Korea

<sup>2</sup>Radiation Instrumentation Research Division, Korea Atomic Energy Research Institute, Daejeon, Korea

<sup>3</sup>R&D Team, PDP Division, Samsung SDI Co. Ltd., Cheonan, Chungcheongnam-Do, Korea

The discharge characteristics, especially the address discharge characteristics, were examined relative to the number of sustain pulse from 2 to 200 applied during the prior sub field under the variable Xe gas conditions (11, 15, and 20%) of plasma display panels (PDPs). As the Xe contents increased from 11 to 20%, the formative delay time was observed to be increased. In particular, as the number of sustain pulse was increased from 2 to 200 during the prior sub field, the formative delay time of the subsequent address discharge was considerably increased under the high Xe (20%) content. Based on this experimental observation, the modified driving waveform, featuring being able to produce a stable address discharge irrespective of the sustain pulse number during the prior sub field, is proposed for the stable address discharge of the high Xe PDP.

**Keywords** MgO layer; discharge characteristics; plasma application; plasma display panel

#### 1. Introduction

For the realization of the full high-definition plasma display panels, the high-speed address has become one of the most important issues, especially under the address-display-separated (ADS) driving method [1, 2]. The full color images are displayed as a result of superposition of the on- and off-cell states during one TV-field. Thus, the successful display of various images strongly depends on how uniformly the wall charges on three electrodes maintain among the subfields with a different number of sustain pulse. The non-uniform wall charge variation causes the unstable address discharge [2, 3].

Moreover, as the Xe content increases to improve luminous efficiency, the address discharge delay time becomes much longer. In this sense, the maintenance of the constant

<sup>\*</sup>Address correspondence to Prof. Heung-Sik Tae, School of Electronics Engineering, College of IT Engineering, Kyungpook National University, Sangyuk-dong, Buk-gu, Daegu 702-701, Korea (ROK). E-mail: hstae@ee.knu.ac.kr

Color versions of one or more of the figures in the article can be found online at www.tandfonline.com/gmcl.

wall voltage within the cells among the subfields is very important factor for the high-speed address in the high Xe condition [4, 5].

Accordingly, in this paper, it was investigated to know the address discharge characteristic under the high Xe condition. Also, the wall voltage distribution after the reset-period using the V<sub>t</sub> closed-curve method was investigated to explain the difference of the address discharge characteristic according to the Xe content. Based on the address discharge characteristics and the wall voltage distribution relative to the Xe content, the experiment changing the hold time and the slope of falling reset in the selective reset-period to improve the address discharge delay in the high Xe condition is progressed.

#### 2. Experimental Methods

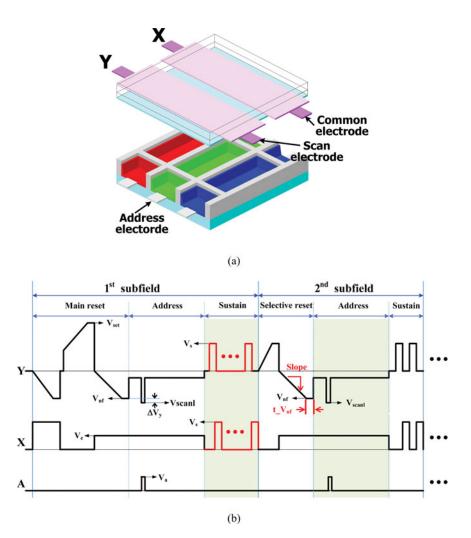

Figure 1 (a) shows the single pixel structure of the 42-in. HD AC-PDP panel with three electrodes, where X is the common electrode, Y is the scan electrode, and A is the address

Figure 1. Schematic diagram of single pixel from 42-in. HD PDP employed in this experiment.

|                      | <u> </u>                         |                                                                                                                        |  |  |

|----------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|

| el                   | Rear panel                       |                                                                                                                        |  |  |

| 225 μm               | Barrier rib width                | 55 μm                                                                                                                  |  |  |

| $85~\mu\mathrm{m}$   | Barrier rib height               | $120~\mu\mathrm{m}$                                                                                                    |  |  |

| $50  \mu \mathrm{m}$ | Address width                    | $95~\mu\mathrm{m}$                                                                                                     |  |  |

|                      | 912 $\mu$ m × 693 $\mu$ m        |                                                                                                                        |  |  |

|                      | 420 Torr                         |                                                                                                                        |  |  |

|                      | Ne-He (35%)-Xe (11, 15, and 20%) |                                                                                                                        |  |  |

|                      | 225 μm<br>85 μm                  | 225 $\mu$ m  85 $\mu$ m  Barrier rib width  85 $\mu$ m  Barrier rib height  Address width  912 $\mu$ m × 693  420 Torr |  |  |

**Table 1.** Specifications of 42-in. HD test panel in this study

electrode. The 42-in. test panel with a working gas pressure of 450 torr was employed in the research, and its structure and dimensions were exactly the same as those of a conventional 42-in. HD PDP with a square-type barrier rib. The gas mixture of test panel was He (51%)-Ne-Xe (11, 15, and 20%). The cell conditions of test panels were exactly the same, except for Xe content condition. The detail panel specifications are listed in Table 1. Figure 1 (b) shows the driving waveforms employed in this study. The various voltages used in the study and voltage level in Figure 1 (b) are shown in Table 2. To equalize the firing voltage condition between the A-Y electrodes after the selective reset-period, the voltages of reset-period such as  $V_{\rm nf}$ ,  $V_{\rm e}$  were same in all Xe contents.

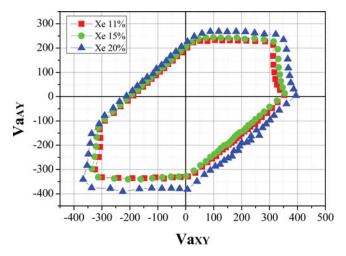

Figure 2 shows the  $V_t$  closed curves measured at three different Xe contents under zero initial wall-voltage conditions. When the Xe-gas content was increased from 11 to 20%, the area of the  $V_t$  closed curve was enlarged, meaning that the firing voltages among the three electrodes increased in proportion to the Xe content.  $V_{f\_AY}$  was 230 V on Xe 11%, 242 V on Xe 15% and 267 V on Xe 20%.  $V_{f\_XY}$  was 314 V on Xe 11%, 332 V on Xe 15% and 365 V on Xe 20%.

#### 3. Results and Discussion

## 3.1. Characteristics of Address Discharge Delay Time Relative to Number of Sustain Pulses Applied During Prior Subfield under Variable Xe Contents

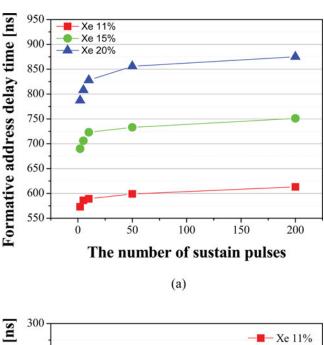

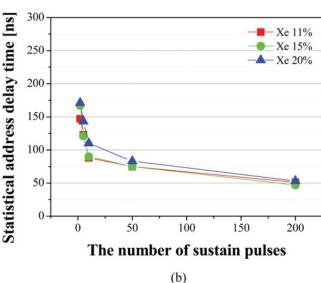

Figures 3 (a) and (b) show the address discharge characteristics relative to the number of sustain pulses applied during the prior subfield under various Xe contents. As shown in Fig. 3 (a), the formative delay time  $(T_f)$  was increased as the Xe content was increased. In particular, as the number of sustain pulse applied during prior subfield was increased from 2 to 200, the  $T_f$  was observed to be considerably increased under the high Xe (20%) content. The  $T_f$  was increased by 40 ns in Xe 11%, by 61 ns in Xe 15%, and by 88 ns in Xe 20% with an increase in the sustain pulse number from 2 to 200. This result indicates that

**Table 2.** Various voltages used in the study and voltage level

| $\overline{\mathbf{V}_{\mathrm{s}}}$               | V <sub>set</sub>                       | 365 V        | $V_{senl}$                                                                         | -205 V         |

|----------------------------------------------------|----------------------------------------|--------------|------------------------------------------------------------------------------------|----------------|

| 205 V (Xe 11%)<br>210 V (Xe 15%)<br>215 V (Xe 20%) | $egin{array}{c} V_e \ V_a \end{array}$ | 80 V<br>55 V | $\begin{array}{c} V_{nf} \\ \Delta V_{y} (= V_{nf} \text{-} V_{senl}) \end{array}$ | -185 V<br>20 V |

**Figure 2.** Driving waveform employed in this experiment.

the  $T_f$  is closely related to the number of sustain pulse applied during the prior subfield, especially under high Xe contents.

Whereas, Fig. 3 (b) shows that the variation of statistical delay time  $(T_s)$  was almost similar in all high Xe contents, and the  $T_s$  was decreased with an increase in the number of sustain pulses applied during the prior subfield. The experimental result of Figure 3 (b) can be explained by the well-known fact that the  $T_s$  strongly depends on the presence of priming particles, and the number of the discharge produced during the prior sustain period can influence the life time of priming particles during the subsequent address discharge.

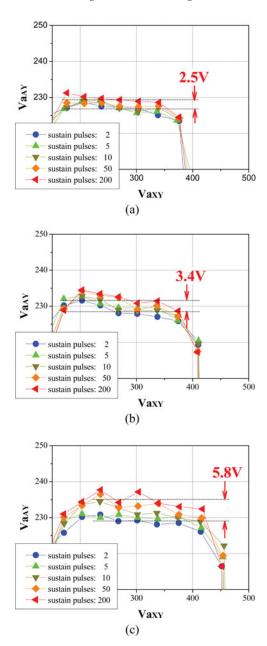

These formative delay characteristics are closely related to the wall voltage loss between the A-Y electrodes after selective reset period [6, 7]. Accordingly, to analyze the changes in the wall voltage after selective reset-period relative to the number of sustain pulses applied during the prior subfield under various Xe contents, the V<sub>t</sub> closed curve was measured [7-9]. Figures 4 (a), (b), and (c) show the V<sub>t</sub> closed curves after selective reset period relative to the number of sustain pulses applied during the prior subfield under various Xe contents (11, 15, and 20%). With an increase in the sustain pulse number during the prior subfield and Xe content, the difference of cell voltage between the A-Y electrodes was observed to be increased. In particular, for high Xe content of 20%, the difference of cell voltage between the A-Y electrodes showed the maximal change, as shown in Fig. 4 (c). This result means that the firing voltage between the A-Y electrodes was increased during the selective reset period due to the increase in the wall voltage loss induced by the increase in the sustain pulse number during the prior sub field [10, 11]. Consequently,  $T_f$ was increased with an increase in the sustain pulse number. Based on these experimental observations, to improve the address discharge delay characteristic, two parameters in the selective reset waveform of Fig. 1 (b), i.e., the hold time (t\_V<sub>nf</sub>) and voltage slope of the falling reset waveform were modified.

## 3.2. Modified Driving Waveform for Stable Address Discharge under Various Sustain Pulse Numbers

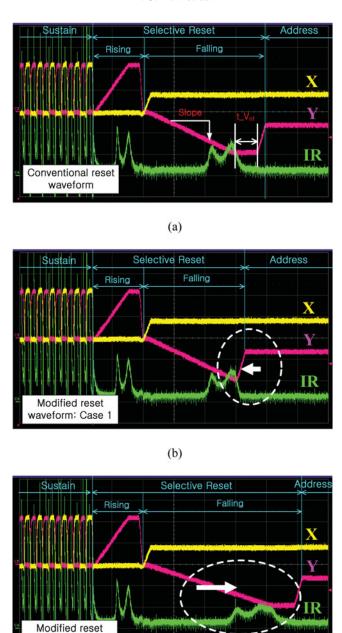

Figure 5 shows the modified selective reset waveforms to equalize the address discharge delay among the subfields with the variable number of sustain pulses under the high Xe condition. As the  $T_f$  is determined by the cell voltage, Figs. 5 (b) and (c) show two cases

Figure 3. Vt closed curves measured at three different Xe contents under zero initial wall-voltage conditions.

of the modified selective reset waveform proposed in such a way that the difference of cell voltage can be minimized irrespective of the number of sustain pulses applied during the prior sub field.

Figure 5 (b) shows the modified selective reset waveform with short hold time during the falling reset period for reducing the wall charge loss between the A-Y electrodes. The IR emission was cut at the end of falling reset period in the first modified waveform (Case 1) as compared with the conventional selective reset waveform. Figure 5 (c) shows the modified selective reset waveform with a slow slope during falling reset period for reducing the wall charge loss between the A-Y electrodes. The peak of IR emission during falling reset period

**Figure 4.** Address discharge delay time relative to number of sustain pulses applied during prior subfield under variable Xe contents: (a) Xe 11%, (b) Xe 15%, (c)Xe 20%.

was reduced by producing the weak discharge due to the slower voltage slope of the second modified waveform (Case 2) as compared with the conventional selective reset waveform.

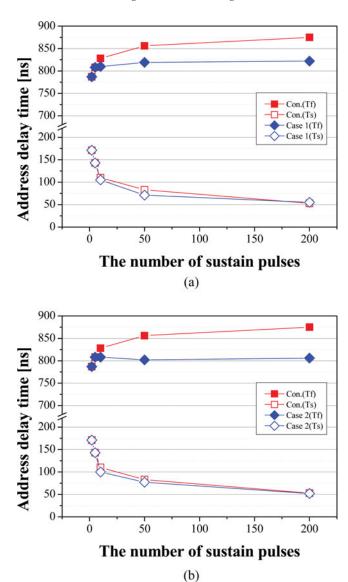

Figure 6 shows the variations in the address discharge delays including the  $T_f$  and  $T_s$  when adopting the two modified reset waveforms in Figs. 5 (b) and (c). To equalize the cell voltage between the A-Y electrodes relative to the sustain pulses number, the hold time,  $t_-V_{nf}$  of the proposed first modified reset waveform was fixed at 15  $\mu$ s in the case of the

**Figure 5.** Modified reset waveforms to equalize address discharge delay among subfields: (a) conventional reset waveform, (b) modified reset waveform with short hold time of falling reset, and (c) modified reset waveform with slow slope of falling reset.

(C)

waveform: Case 2

**Figure 6.** Address delay time relative to number of sustain pulse measured when applying modified driving waveform under Xe 20% condition: (a) case 1 and (b) case 2.

**Table 3.** Variation of formative delay time after applying the modified reset waveform of Case 1

| The number of sustain pulses | 2  | 5  | 10 | 50 | 200 |

|------------------------------|----|----|----|----|-----|

| $t_{-}V_{nf}[\mu s]$         | 15 | 15 | 2  | 2  | 2   |

| Decreased delay time [ns]    | 0  | 0  | 18 | 37 | 53  |

| Case 2                       |     |     |     |     |     |

|------------------------------|-----|-----|-----|-----|-----|

| The number of sustain pulses | 2   | 5   | 10  | 50  | 200 |

| Slope rate $[V/\mu s]$       | 3.3 | 3.3 | 2.3 | 2.3 | 2.3 |

| Decreased delay time [ns]    | 0   | 0   | 20  | 54  | 69  |

**Table 4.** Variation of formative delay time after applying the modified reset waveform of

sustain pulse number from 2 to 5, which was exactly the same as the conventional case,  $2 \mu s$  in case of the sustain pulse number from 100 to 200. As a result of adjusting the hold time according to the sustain pulse number, the  $T_f$  was reduced by 53 ns for the sustain pulse number of 200, when compared with conventional case, as shown in Table 3 and Fig. 6 (a).

In the second modified reset waveform (Case 2), the voltage slope of the falling resetperiod was fixed at 3.3 V/ $\mu$ s in the case of the sustain pulse number from 2 to 5, which was exactly the same as the conventional case, 2.3 V/ $\mu$ s in case of the sustain pulse number from 100 to 200. As a result of adjusting the voltage slope according to the sustain pule number, the  $T_f$  was reduced by 69 ns for the sustain pulse number of 200, when compared with conventional case, as shown in Table 4 and Fig. 6 (b).

#### Conclusion

In this paper, the address discharge characteristics depending on the number of the sustain pulse applied during the prior subfield were monitored, by increasing the sustain pulse number from 2 to 200 under the variable Xe gas conditions (11, 15, and 20%) of the 42 inch plasma displays panels (PDPs). This experimental result confirms that the variations in both the formative delay time ( $T_f$ ) and the statistical delay time ( $T_s$ ) depend on the number of sustain pulses applied during the prior subfield. Under high Xe condition (20%), the  $T_f$  shows the maximal change according to the sustain pulse number because the wall voltage loss occurs maximally between the A-Y electrodes during the selective reset period. In order to minimize  $T_f$  under high Xe content (20%), two modified selective reset waveforms are proposed, one of which has a feature of longer hold time, the other of which has a feature of slower voltage slope during the falling reset period. In particular, when applying the modified reset waveform with slower voltage slop (Case 2), the variation of  $T_f$  is more effectively suppressed regardless of the variation in the sustain pulse number by producing the weak discharge due to slower voltage slope during the falling reset period.

#### Funding

This research was supported by Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (2013R1A1A4A03008577).

#### References

- [1] Park, C.-H., Lee, S.-H., Kim, D.-H., Lee, W.-G., & Heo, H.-E. (2001). *IEEE Trans. Elec., Dev.*, 48, 2260

- [2] Kim, J. S., Yang, J. H., Kim, T. J., & Whang, K.-W. (2003). IEEE Trans. Plasma Sci., 31, 1083.

- [3] Shin, B. J., Choi, K. C., & Seo, J. H. (2005). IEEE Trans. Electron Devices, 52, 17.

- [4] Tae, H.-S., Jang, S.-K., Cho, K.-D., & Park, K.-H. (2006). IEEE Trans. Elec. Dev., 53, 196.

- [5] Cho, K. H., Lee, S.-M., & Choi, K. C., (2007). IEEE Trans. Plasma Sci., 35, 1567.

- [6] Jang, S.-K., Park, C.-S., & Tae, H.-S. (2011). Mol. Cryst. Liq. Cryst., 551, 86.

- [7] Park, H. D., Kim, J. H., Tae, H.-S., & Kim, B.-S. (2013). Mol. Cryst. Liq. Cryst., 585, 25.

- [8] Sung, C. H., Kim, J. H., Chung, Y. C., Jeon, M. J., Seo, J. W., Jung, Y. K., & Kang, B. K. (2012). *Displays*, 33, 21.

- [9] Jang, S.-K., Park, C.-S., & Tae, H.-S. (2010). IEEE Trans. Elec. Dev., 57, 3213.

- [10] Kim, J. K. (2013). IEEE Trans. Elec. Dev., 60, 2556.

- [11] Kim, J.-Y., Jeng, Y. T., & Cho, B.-G. (2011). IEICE Trans. Electron., E94-C, 1483.